## AN FPGA-BASED ON-BOARD MULTI/HYPERSPECTRAL IMAGE COMPRESSION SYSTEM

Guoxia Yu<sup>1</sup>, Tanya Vladimirova<sup>1</sup>, and Martin Sweeting<sup>1,2</sup>

<sup>1</sup>Surrey Space Centre, University of Surrey, Guildford, GU2 7XH, United Kingdom <sup>2</sup>Surrey Satellite Technology Limited, Surrey Research Park, Guildford, GU2 7YE, United Kingdom

## **1. INTRODUCTION**

Earth Observation satellites require transmission to ground of an extensive amount of imaging data. The data generation capability of the on-board instruments these days is reaching several times that of the downlink transmission capacity. Data compression is believed to be the solution to the "Bandwidth Versus Data Volume" dilemma of modern spacecraft [1]. On the other hand, recent fast advances in Field Programmable Gate Arrays (FPGAs), such as high clock frequencies and parallel processing capabilities, have made them a preferred platform for high performance computing tasks, like multi/hyperspectral image compression. In addition, FPGAs can be considered a flight-proven technology, as they have been used in a number of space missions, ranging from control and data processing tasks in satellites to Mars rovers .

In current on-board compression systems, multispectral images are mostly processed band-by-band [2], which is referred to as intra-band compression. Spectral redundancy that is found specifically in multispectral images can be removed via spectral decorrelation. Although spectral decorrelation has been actively investigated in the literature, it has not yet been applied to on-board multispectral image compression. Based on the survey and development trends in [2], an on-board compression system for multi/hyperspectral images is proposed, which comprises pre-processing, spectral decorrelation, and compression blocks. For the purpose of high-performance on-board computing an efficient hardware implementation is achieved using FPGA-based acceleration.

## 2. COMPRESSION SYSTEM DESCRIPTION

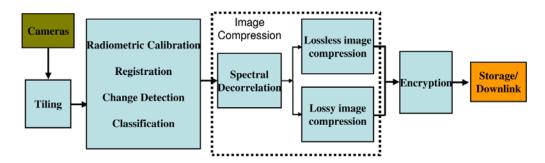

The architecture of the proposed on-board image compression system is shown in Figure 1. The raw image data, after coming out of the cameras, is processed serially, tile-by-tile, initially undergoing some pre-processing tasks, which improve compression performance and enable the system to make intelligent decisions about the compression process.

Radiometric calibration is achieved via the Brightness Difference Compensation (BDC) method, which is an exactly lossless technique showing good performance [3]. In [4] a gradient-image based phase correlation (GradPC) technique for band registration is proposed, which features increased accuracy and robustness. GradPC has a failure detection mechanism, which detects the cases when it fails to find the right displacement and has zero false-positive rates. This failure happens on homogenous areas such as sea water or heavy clouded areas. Therefore GradPC could virtually function like a simple classifier detecting homogenous areas, i.e. Regions of Non-interest. The Karhunen-Loeve Transform (KLT) is adopted for spectral decorrelation. A lossless compression scheme [5], which is based on an extended Rice algorithm, is used to efficiently compress panchromatic and multi/hyperspectral images. For lossy image compression, data can be encrypted, before being downlinked to the ground station or stored on board according to a store-and-forward scheme. Each processing module in Figure 1 is optional and can be omitted. It is also possible to preserve the uncompressed raw image data.

## **3. FPGA-BASED HARDWARE ACCELERATION**

A hardware acceleration design flow based on the Xilinx AccelDSP tool is adopted [6]. First a high-level floating-point Matlab model is developed and verified and then AccelDSP is used to analyze and convert it into a hardware description language (HDL) design. The model is developed according to a clearly defined algorithmic flow taking into account how it will be translated into HDL and how it will operate on the FPGA chip. This allows the user to configure the bit-length of the datapath and the critical registers and carry out optimization at the algorithmic level.

Figure 1: Block diagram of the proposed on-board image compression system

|                                              |                                             | <u> </u>                        |

|----------------------------------------------|---------------------------------------------|---------------------------------|

| Table 1. Characteristics of the lossless con | pression hardware design for different FPGA | families and datanath hitlength |

| Table 1. Characteristics of the lossiess con |                                             | and datapath bittength          |

| Designs           | Design A          | Design B               | Design C            | CAST JPEG-LS        |

|-------------------|-------------------|------------------------|---------------------|---------------------|

| FPGA              | 8 bits/pixel      | 12 bits/pixel          | 16 bits/pixel       | 8bits/pixel         |

| Spartan3E 1200E-5 | 3615 Slices @113M | Hz 5378 Slices @80MHz  | 6820 Slices @80MHz  | 5636 Slices @64MHz  |

| Virtex4 LX25-12   | 3457 Slices @224M | Hz 5317 Slices @179MHz | 6789 Slices @166MHz | 5591 Slices @112MHz |

| Virtex5 LX30-3    | 1638 Slices @282M | Hz 2554 Slices @250MHz | 2950 Slices @210MHz | 2182 Slices @166MHz |

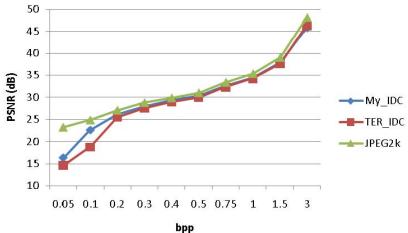

Figure 2: PSNR v.s. bpp of CCSDS-IDC(My\_IDC), TER\_IDC and JPEG2000

The hardware design is improved by using advanced techniques, such as pipelining, supreme quantization, and a multiplierfree design. Characteristics of the hardware implementation for the lossless compression block are given in Table 1, where CAST JPEG-LS is a reference implementation, included for comparison purposes. The developed accelerator can achieve a throughput of around 200 Mpixels/second with low chip area occupancy and low power consumption. Matlab modeling of the CCSDS-IDC algorithm has shown that its performance is comparable to JPEG2000 and TER\_IDC (an existing CCSDS-IDC software implementation), as illustrated in Figure 2. A reconfigurable System-on-a-Chip design based on the LEON3 soft processor is developed for payload computing targeting the small satellite platform [6].

[1] T. Vladimirova, M. Meerman, and A. Curiel, "On-Board Compression of Multispectral Images for Small Satellites," in *IEEE International Conference on Geoscience and Remote Sensing Symposium, 2006. IGARSS 2006.*, 2006, pp. 3533-3536.

[2] G. Yu, T. Vladimirova, and M. Sweeting, "Image Compression Systems on Board Satellites," to appear in Acta Astronautica, 2009.

[3] G. Yu, T. Vladimirova, and M. Sweeting, "A New Automatic On-Board Multispectral Image Compression System for Leo Earth Observation Satellites," in 2007 15th IEEE International Conference on Digital Signal Processing, 2007, pp. 395-398.

[4] G. Yu, T. Vladimirova, and M. Sweeting, "Autonomous Band Registration for On-Board Applications," in 2007 IEEE International Conference on Signal Processing and Communications, Dubai, UAE, 2007, pp. 1327-1330.

[5] G. Yu, T. Vladimirova, and M. N. Sweeting, "An Efficient On-Board Lossless Compression Design for Remote Sensing Image Data," in *IEEE International Geoscience & Remote Sensing Symposium, IGARSS 2008*, Boston, Massachusetts, U.S.A., 2008.

[6] G. Yu, T. Vladimirova, X. Wu, and M. N. Sweeting, "A New High-Level Reconfigurable Lossless Image Compression System for Space Applications," in *NASA/ ESA Conference on Adaptive Hardware and Systems. AHS-2008.*, ESTEC, Noordwijk, The Netherlands, 2008.